probe tcl syntax to save variables inside automatic tasks in systemverilog - Functional Verification - Cadence Technology Forums - Cadence Community

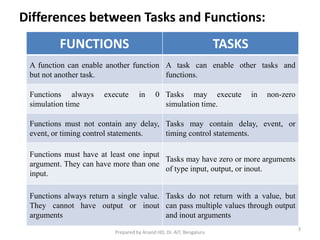

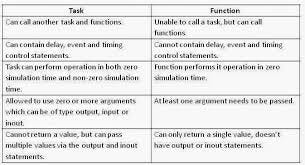

2. Functions and Tasks (call by reference) , automatic keyword, timescale in SystemVerilog - YouTube

Systemverilog语言(5)-------Procedural statements and Routiness_system verilog procedural_Chauncey_wu的博客-CSDN博客

verilog - How to understand which SystemVerilog is supported by Cadence XMVLOG compiler? - Stack Overflow

A SystemVerilog DPI Framework for Reusable Transaction Level Testing, Debug and Analysis of SoC Designs